PhoneArena 에 따르면, 2025년에 TSMC와 Samsung Foundry가 2nm 칩의 양산을 시작할 것으로 예상되며, 이는 1.8nm 칩을 통해 인텔이 칩 제조 공정을 선도할 수 있다는 것을 의미합니다. 인텔은 EUV 고NA 머신당 3억~4억 달러를 지출할 것으로 알려졌습니다.

ASML High-NA 기계 한 대당 가격은 최소 3억 달러입니다.

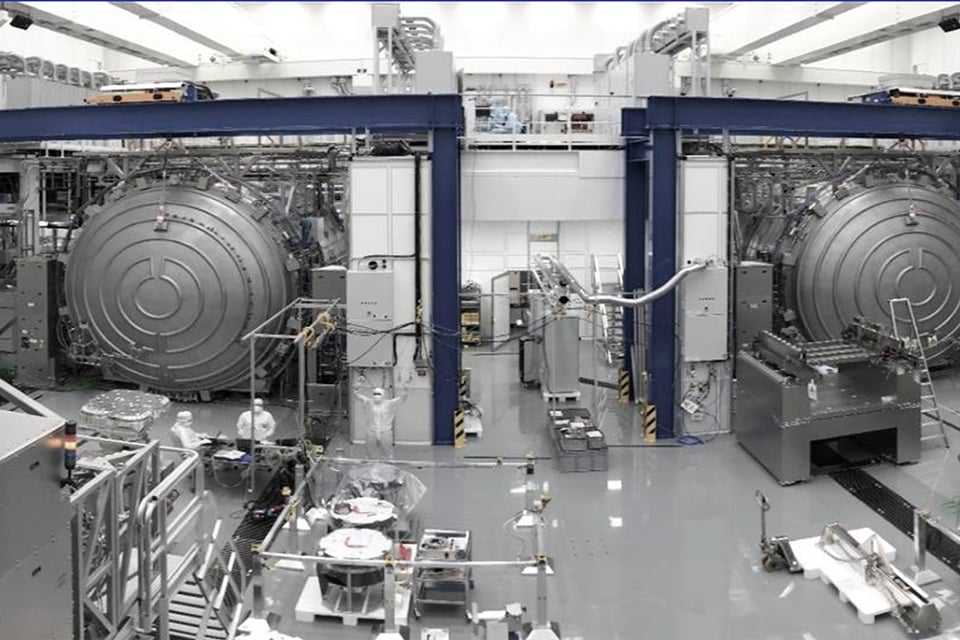

ASML은 배송에 대해 다음과 같이 말했습니다. "우리는 첫 번째 High-NA 시스템을 배송하고 있으며 이를 소셜 미디어 게시물에서 발표했습니다. 이 시스템은 이전에 발표된 대로 계획대로 인텔에 제공될 것입니다."

고 NA 시스템에서는 NA 숫자가 높을수록 실리콘 웨이퍼에 식각된 패턴의 해상도가 높아집니다. 현재 EUV 기계는 .33 조리개(13nm 분해능과 동일)를 가지고 있는 반면, 고 NA 기계는 .55 조리개(8nm 분해능과 동일)를 가지고 있습니다. 더 높은 해상도의 패턴이 웨이퍼에 전송되면, 주조소는 추가 기능을 추가하기 위해 웨이퍼를 EUV 장비에 두 번 통과시킬 필요가 없어져 시간과 비용을 모두 절약할 수 있습니다.

고 NA EUV 기계는 주로 트랜지스터의 크기를 줄이고 밀도를 높여 칩 내부에 더 많은 트랜지스터를 넣는 데 중점을 둡니다. 칩에 트랜지스터가 많을수록 더욱 강력하고 에너지 효율이 높습니다. High-NA 장비를 사용하면 트랜지스터 크기를 1.7배 줄일 수 있고 밀도는 2.9배 증가합니다.

각 High-NA 기계는 ASML에서 13개의 대형 컨테이너로 운송됩니다.

새로운 버전의 High-NA EUV 장비는 2nm 이하 칩 제조 공정을 실현하는 데 도움이 될 것입니다. 바로 지난주에 TSMC와 Samsung Foundry가 2nm 이후 로드맵을 발표했습니다. 두 회사는 2027년까지 1.4nm 공정을 사용하여 반도체를 개발할 계획입니다. 2nm 칩 생산은 2025년에 시작될 예정이며, 며칠 전 TSMC는 Apple이 2nm 칩 프로토타입을 평가하도록 허용했습니다.

EUV 고NA 장비를 운반하는 것은 13개의 대형 컨테이너와 250개의 상자에 나뉘어져 있었기 때문에 쉬운 일이 아니었습니다. 기계를 조립하는 것 역시 매우 어려웠습니다.

[광고2]

소스 링크

댓글 (0)