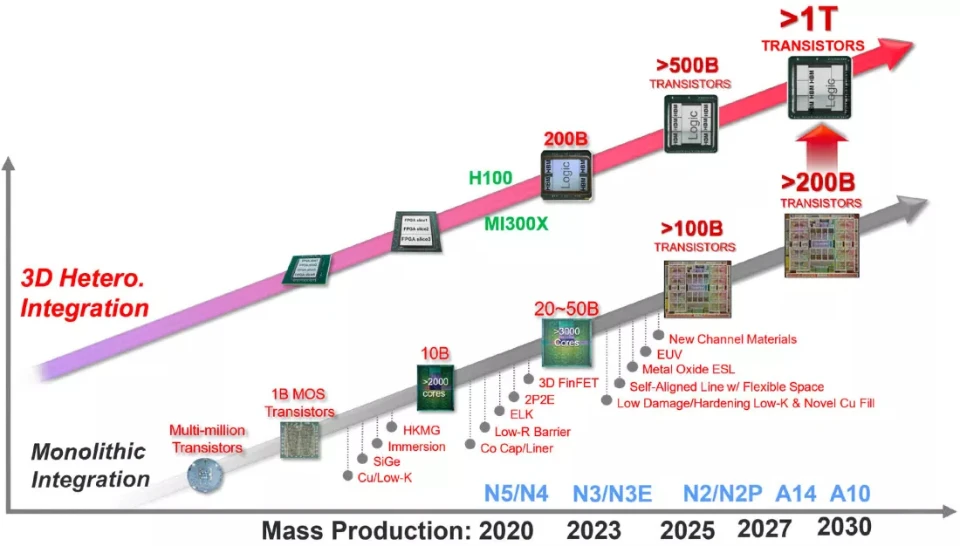

Techspotによると、TSMC は最近の IEDM カンファレンスで、次世代半導体製造プロセスの製品ロードマップを発表しました。このロードマップは、最終的には単一のチップ パッケージに 1 兆個のトランジスタを搭載した複数の 3D スタック チップレット設計を提供することになります。 CoWoS、InFO、SoIC などのパッケージング技術の進歩により、同社はこの目標を達成できるようになり、2030 年までにモノリシック設計で 2,000 億個のトランジスタを実現できると TSMC は考えています。

TSMCは2030年までに1nmチップを製造できると考えている

Nvidia の 800 億個のトランジスタを搭載した GH100 は、現在市場にある最も複雑なモノリシック チップの 1 つです。しかし、これらのチップのサイズが大きくなり、価格も高くなるにつれて、TSMC は、メーカーが、AMD が最近発売した Instinct MI300X や、1,000 億個のトランジスタを持つ Intel の Ponte Vecchio などのマルチチップレット アーキテクチャを採用するようになるだろうと考えています。

今のところ、TSMC は 2nm N2 および N2P 製造プロセスと、1.4nm A14 および 1nm A10 チップの開発を継続します。同社は2025年末までに2nmの生産を開始する予定。2028年には1.4nmのA14プロセスに移行し、2030年までに1nmトランジスタの生産を計画している。

一方、Intel は 2nm (20A) および 1.8nm (18A) プロセスに取り組んでおり、これらは同じ時期に発売される予定です。新しいテクノロジーの利点の 1 つは、ロジック密度の向上、クロック速度の向上、電力リークの低減を実現し、よりエネルギー効率の高い設計につながることです。

TSMCの次世代先進チップ開発の目標

世界最大のファウンドリーであるTSMCは、自社の製造プロセスがどのIntel製品よりも優れていると確信している。 TSMCの最高経営責任者(CEO)CC・ウェイ氏は決算発表で、社内調査により同社のN3P技術と3nm製造プロセスの改善が確認され、「PPAはインテルの18Aプロセスに匹敵する」ことが実証されたと述べた。彼は、N3P がさらに優れたものとなり、競争力が高まり、コスト面で大きな優位性を持つようになることを期待しています。

一方、インテルのCEO、パット・ゲルシンガー氏は、同社の18A製造プロセスは1年前にリリースされたTSMCの2nmチップを上回る性能を発揮すると主張した。もちろん、それは時間が経てばわかるでしょう。

[広告2]

ソースリンク

コメント (0)