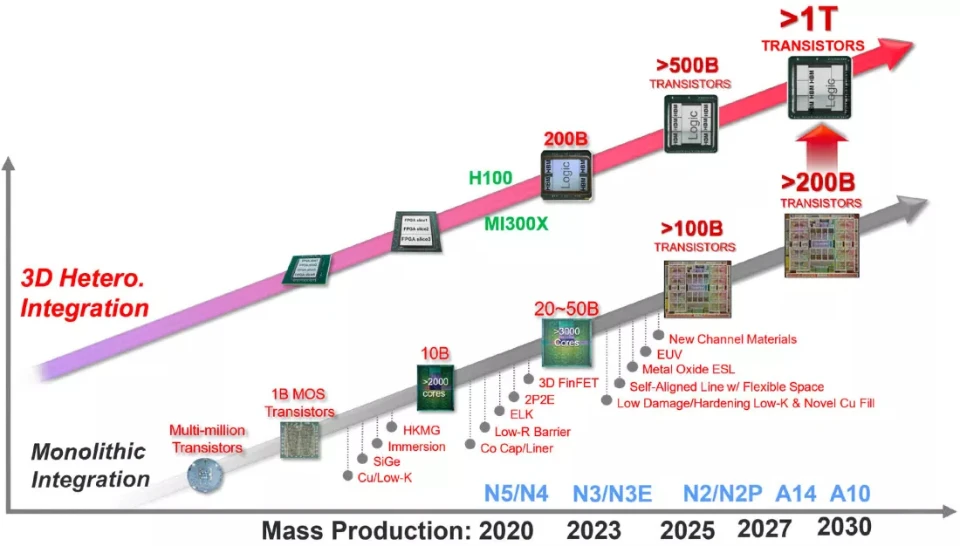

ตามรายงานของ Techspot ที่งานประชุม IEDM เมื่อเร็ว ๆ นี้ บริษัท TSMC ได้ประกาศแผนงานผลิตภัณฑ์สำหรับกระบวนการผลิตเซมิคอนดักเตอร์รุ่นถัดไป ซึ่งจะนำไปสู่การนำเสนอชิปเล็ตแบบ 3D ที่ซ้อนกันหลายตัวโดยมีทรานซิสเตอร์ 1,000 พันล้านตัวในแพ็คเกจชิปตัวเดียวในที่สุด ความก้าวหน้าในเทคโนโลยีบรรจุภัณฑ์ เช่น CoWoS, InFO และ SoIC จะทำให้บริษัทบรรลุเป้าหมายนั้นได้ และภายในปี 2030 TSMC เชื่อว่าการออกแบบแบบโมโนลิธิกของบริษัทจะสามารถเข้าถึงทรานซิสเตอร์ได้ถึง 200 พันล้านตัว

TSMC เชื่อว่าจะสามารถสร้างชิปขนาด 1 นาโนเมตรได้ภายในปี 2030

ชิป GH100 ที่มีทรานซิสเตอร์ 80 พันล้านตัวของ Nvidia ถือเป็นชิปโมโนลิธิกที่มีความซับซ้อนที่สุดในตลาดปัจจุบัน อย่างไรก็ตาม เนื่องจากชิปเหล่านี้มีขนาดใหญ่ขึ้นและมีราคาแพงขึ้น TSMC เชื่อว่าผู้ผลิตจะนำสถาปัตยกรรมชิปหลายตัวมาใช้ เช่น Instinct MI300X ของ AMD ที่เพิ่งเปิดตัว และ Ponte Vecchio ของ Intel ซึ่งมีทรานซิสเตอร์ 100 พันล้านตัว

ในขณะนี้ TSMC จะพัฒนากระบวนการผลิต N2 และ N2P ขนาด 2 นาโนเมตรต่อไป เช่นเดียวกับชิป A14 และ A10 ขนาด 1.4 นาโนเมตรต่อไป บริษัทวางแผนที่จะเริ่มการผลิต 2 นาโนเมตรภายในสิ้นปี 2025 ในปี 2028 บริษัทจะเปลี่ยนไปใช้กระบวนการ A14 ขนาด 1.4 นาโนเมตร และภายในปี 2030 บริษัทมีแผนที่จะผลิตทรานซิสเตอร์ขนาด 1 นาโนเมตร

ขณะเดียวกัน Intel กำลังพัฒนากระบวนการผลิตขนาด 2 นาโนเมตร (20A) และ 1.8 นาโนเมตร (18A) ซึ่งคาดว่าจะเปิดตัวในช่วงเวลาเดียวกัน ข้อดีอย่างหนึ่งของเทคโนโลยีใหม่ก็คือความหนาแน่นของตรรกะที่สูงขึ้น ความเร็วสัญญาณนาฬิกาที่เพิ่มขึ้น และการรั่วไหลของพลังงานที่น้อยลง นำไปสู่การออกแบบที่มีประสิทธิภาพในการใช้พลังงานมากยิ่งขึ้น

เป้าหมายของ TSMC ในการพัฒนาชิปขั้นสูงรุ่นต่อไป

เนื่องจาก TSMC เป็นโรงหล่อที่ใหญ่ที่สุดในโลก เราจึงมั่นใจว่ากระบวนการผลิตของตนจะมีประสิทธิภาพเหนือกว่าผลิตภัณฑ์ใดๆ ของ Intel ในการประชุมผลประกอบการ CC Wei ซีอีโอของ TSMC กล่าวว่าการตรวจสอบภายในได้ยืนยันถึงการปรับปรุงในเทคโนโลยี N3P ของบริษัทและกระบวนการผลิต 3 นาโนเมตร ซึ่งแสดงให้เห็นว่า "PPA นั้นเทียบได้กับ" กระบวนการ 18A ของ Intel เขาหวังว่า N3P จะดีขึ้นกว่าเดิม มีการแข่งขันมากขึ้น และมีข้อได้เปรียบด้านต้นทุนอย่างมีนัยสำคัญ

ในขณะเดียวกัน Pat Gelsinger ซีอีโอของ Intel อ้างว่ากระบวนการผลิต 18A ของตนจะเหนือกว่าชิป 2 นาโนเมตรของ TSMC ที่เปิดตัวเมื่อปีที่แล้ว แน่นอนว่าเฉพาะเวลาเท่านั้นที่จะบอกได้

ลิงค์ที่มา

การแสดงความคิดเห็น (0)