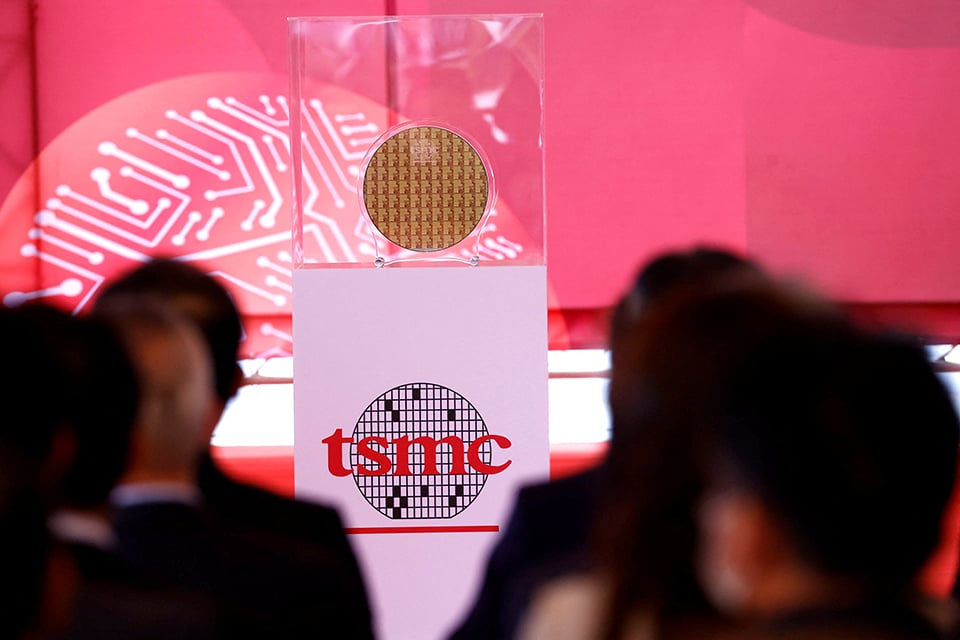

Tech News Space 에 따르면, TSMC CEO Mark Liu는 최근 분석가 및 투자자들과 회의를 갖고 회사의 계획을 공유하며, 2nm 공정 기술을 사용한 칩의 양산이 이르면 2025년에 시작될 것이라는 자신감을 표명했습니다. 그는 TSMC가 증가하는 수요를 충족하기 위해 신주 과학단지와 가오슝(대만)에 여러 제조 시설을 설립하려는 의도를 언급했습니다.

TSMC, 2025년 하반기 2nm 칩 양산 목표

구체적으로 첫 번째 공장은 바오산(신주) 근처, R1 연구 센터 근처에 위치할 예정입니다. R1 연구 센터는 2nm 기술을 개발하기 위해 특별히 설립된 곳입니다. 이 공장은 2025년 하반기에 2nm 반도체의 양산을 시작할 예정입니다. 2nm 칩을 생산하도록 설계된 두 번째 공장은 남부대만과학단지의 일부인 가오슝 과학단지에 들어서며, 2026년에 가동을 시작할 계획입니다.

또한, 회사가 대만 당국의 승인을 받은 후 세 번째 공장을 건설하기 위한 준비가 진행 중입니다.

또한 TSMC는 타이중 과학단지에 또 다른 공장을 건설하기 위해 대만 당국의 승인을 받기 위해 적극적으로 노력하고 있습니다. 2025년에 시설 건설이 시작되면 2027년에 생산이 시작될 예정입니다. 2nm 기술을 사용하여 칩을 생산할 수 있는 3개 공장을 모두 개장함으로써 TSMC는 글로벌 반도체 시장에서의 입지를 크게 강화하고 고객에게 차세대 칩을 생산할 수 있는 새로운 용량을 제공하게 됩니다.

이 회사의 단기 계획에는 2nm 공정 기술로 양산을 시작하는 것이 포함되며, 2025년 하반기에 나노시트 유형의 게이트 올라운드(GAA) 트랜지스터를 사용하는 것이 목표입니다. 2026년에 출시될 예정인 이 공정의 개선된 버전은 칩 뒷면의 전력을 통합하여 양산 능력을 확대할 것입니다.

[광고_2]

소스 링크

![[사진] 녹색성장 및 글로벌 목표 파트너십 제4차 정상회의 폐막](https://vstatic.vietnam.vn/vietnam/resource/IMAGE/2025/4/17/c0a0df9852c84e58be0a8b939189c85a)

![[사진] 토람 사무총장, 베트남 주재 프랑스 대사 올리비에 브로셰 접견](https://vstatic.vietnam.vn/vietnam/resource/IMAGE/2025/4/17/49224f0f12e84b66a73b17eb251f7278)

![[사진] 양국 군대와 국민의 우호, 단결, 협력 증진](https://vstatic.vietnam.vn/vietnam/resource/IMAGE/2025/4/17/0c4d087864f14092aed77252590b6bae)

![[사진] 국회의장 쩐탄만, 석유·가스업계 우수인재들과 만남](https://vstatic.vietnam.vn/vietnam/resource/IMAGE/2025/4/17/1d0de4026b75434ab34279624db7ee4a)

![[사진] 난단신문, '베트남을 너무 사랑해요' 프로젝트 발표](https://vstatic.vietnam.vn/vietnam/resource/IMAGE/2025/4/17/362f882012d3432783fc92fab1b3e980)

![[사진] 중국 국방부 장관 및 우호교류 대표단 환영식](https://vstatic.vietnam.vn/vietnam/resource/IMAGE/2025/4/17/fadd533046594e5cacbb28de4c4d5655)

![[영상] 비엣텔, 베트남 최대 해저 광케이블 라인 공식 가동](https://vstatic.vietnam.vn/vietnam/resource/IMAGE/2025/4/17/f19008c6010c4a538cc422cb791ca0a1)

댓글 (0)