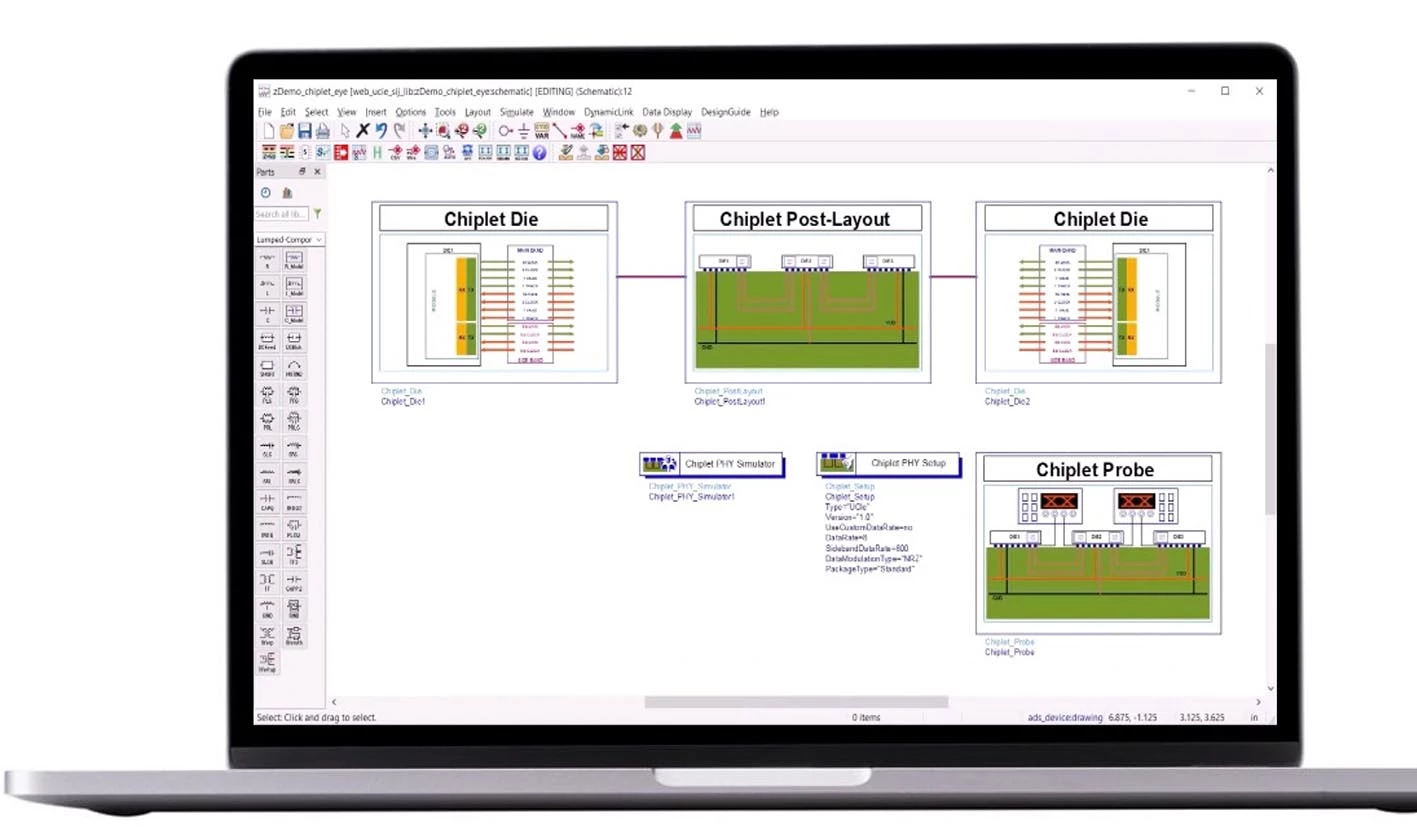

DNVN – Keysight Technologies hat gerade ChipletPHY Designer 2025 auf den Markt gebracht, die neueste digitale Hochgeschwindigkeits-Chiplet-Designlösung, die für KI- und Rechenzentrumsanwendungen geeignet ist.

Diese erweiterte Software fügt Emulationsfunktionen für den Universal Chiplet Interconnect Express™ (UCIe™) 2.0-Standard hinzu und bietet Unterstützung für den Bunch of Wires (BoW)-Standard des Open Computer Project. Als fortschrittliche Chiplet-Design- und Die-to-Die-Designlösung (D2D) auf Systemebene ermöglicht Chiplet PHY Designer die Validierung auf Vorsiliziumebene und vereinfacht so den Chipdesign- und Herstellungsprozess.

Da KI- und Rechenzentrumschips immer komplexer werden, ist eine zuverlässige Kommunikation zwischen den Chips von entscheidender Bedeutung für die Gewährleistung der Leistung.

Der Markt begegnet dieser Herausforderung mit neuen offenen Standards wie UCIe und BoW, um Verbindungen zwischen Chiplets in 2,5D-/3D- oder Overlay-/Enhanced-Packaging zu definieren. Durch die Übernahme dieser Standards und die Überprüfung der Konformität von Chiplets tragen Designer zum Aufbau eines Ökosystems der Chiplet-Interoperabilität bei und reduzieren so Kosten und Risiken bei der Entwicklung von Halbleitertechnologien.

Hauptvorteile von Chiplet PHY Designer 2025: Interoperabilität sicherstellen: Überprüfen Sie, ob die Designs den UCIe 2.0- und BoW-Standards entsprechen, und ermöglichen Sie so eine nahtlose Integration in fortschrittliche Verpackungsökosysteme.

Verkürzen Sie die Markteinführungszeit: Automatisieren Sie die Simulation und die Einrichtung von Konformitätstests und vereinfachen Sie so den Chiplet-Designprozess.

Verbessern Sie die Designgenauigkeit: Erhalten Sie Einblicke in die Signalintegrität, Bitfehlerrate (BER) und Übersprechanalyse und minimieren Sie so das Risiko eines Neudesigns und einer Neuherstellung des Chips.

Optimiertes Taktdesign: Unterstützt erweiterte Taktschemaanalysen, wie z. B. Vierteldatenrate QDR, für eine präzise Synchronisierung bei Hochgeschwindigkeitsverbindungen.

„Vor einem Jahr hat Keysight EDA den Chiplet PHY Designer als erstes Pre-Silicon-Validierungstool auf dem Markt mit umfassenden Modellierungs- und Simulationsfunktionen auf den Markt gebracht“, sagte Hee-Soo Lee, Leiter der Kundenentwicklung für das High-Speed-Digital-Segment bei Keysight EDA. Mit diesem Tool können Chiplet-Designer vor der Herstellung schnell überprüfen, ob ihre Designs den Spezifikationen entsprechen. Die neueste Version erfüllt sich entwickelnde Standards wie UCIe 2.0 und BoW und bietet neue Funktionen wie QDR-Taktmapping und System-Übersprechanalyse für unidirektionale Busse. Ingenieure verwenden den Chiplet PHY Designer, um Zeit zu sparen und Fehler zu reduzieren. Sie stellen sicher, dass ihre Designs vor der Herstellung die Leistungsanforderungen erfüllen. Frühe Anwender dieser Lösung, wie beispielsweise Alphawave Semi, bestätigen, dass Chiplet PHY Designer einen reibungslosen Betrieb und die Interoperabilität der 2,5D/3D-Lösungen gewährleistet, die ihren Chiplet-Kunden zur Verfügung stehen.“

Thanh Van

[Anzeige_2]

Quelle: https://doanhnghiepvn.vn/cong-nghe/cong-nghe-ho-tro-thiet-ke-chip-ky-thuat-so-toc-do-cao/20250205033256204

Kommentar (0)