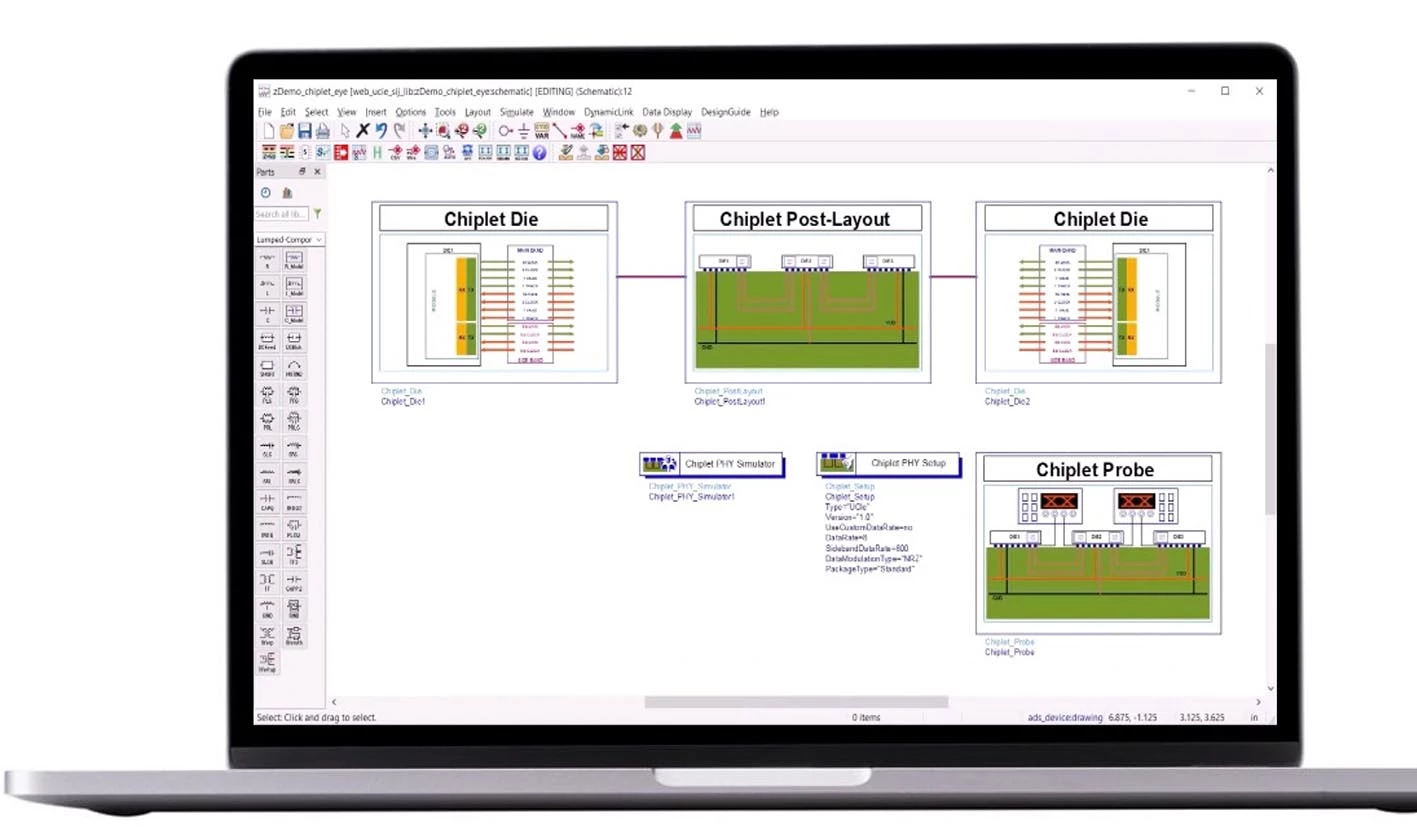

أطلقت شركة DNVN - Keysight Technologies للتو ChipletPHY Designer 2025، وهو أحدث حل لتصميم الشرائح الرقمية عالية السرعة، والمناسب لتطبيقات الذكاء الاصطناعي ومركز البيانات.

تضيف هذه البرامج المحسّنة ميزات المحاكاة لمعيار Universal Chiplet Interconnect Express™ (UCIe™) 2.0 وتضيف الدعم لمعيار Bunch of Wires (BoW) الخاص بمشروع Open Computer Project. باعتباره حلاً متقدمًا لتصميم الشرائح على مستوى النظام وتصميم القالب إلى القالب (D2D)، يتيح Chiplet PHY Designer التحقق على مستوى ما قبل السيليكون، مما يبسط عملية تصميم الشريحة وتصنيعها.

مع تزايد تعقيد الذكاء الاصطناعي وشرائح مراكز البيانات، أصبح الاتصال الموثوق بين الشرائح أمرًا بالغ الأهمية لضمان الأداء.

يعالج السوق هذا التحدي من خلال المعايير المفتوحة الناشئة مثل UCIe وBoW لتحديد الترابطات بين الشرائح في التغليف المحسن/ثلاثي الأبعاد أو التغليف المحسن/ثنائي الأبعاد 2.5. ومن خلال اعتماد هذه المعايير والتحقق من امتثال الشرائح الإلكترونية، يساهم المصممون في بناء نظام بيئي للتوافق بين الشرائح الإلكترونية، مما يقلل التكاليف والمخاطر في تطوير تكنولوجيا أشباه الموصلات.

الفوائد الرئيسية لـ Chiplet PHY Designer 2025: ضمان التشغيل البيني: التحقق من أن التصميمات تلبي معايير UCIe 2.0 وBoW، مما يتيح التكامل السلس عبر أنظمة التغليف المتقدمة.

تقليل الوقت المستغرق لطرح المنتج في السوق: أتمتة عملية إعداد المحاكاة واختبار الامتثال، مما يؤدي إلى تبسيط عملية تصميم الشريحة.

تحسين دقة التصميم: توفير رؤى حول سلامة الإشارة ومعدل خطأ البت (BER) وتحليل التداخل، مما يقلل من مخاطر إعادة التصميم وتصنيع الشريحة.

تصميم ساعة محسن: يدعم تحليل مخطط الساعة المتقدم، مثل معدل البيانات الربعية QDR، لتحقيق مزامنة دقيقة في الاتصالات عالية السرعة.

قال هي سو لي، رئيس تطوير العملاء لقطاع الرقمنة عالية السرعة في شركة Keysight EDA: "قبل عام، أطلقت Keysight EDA برنامج Chiplet PHY Designer كأول أداة للتحقق من صحة ما قبل السيليكون في السوق مع إمكانيات النمذجة والمحاكاة المتعمقة". تتيح هذه الأداة لمصممي الشرائح الصغيرة التحقق بسرعة من أن تصميماتهم تلبي المواصفات قبل التصنيع. يتوافق الإصدار الأحدث مع المعايير المتطورة مثل UCIe 2.0 وBoW، ويوفر ميزات جديدة مثل تعيين ساعة QDR وتحليل التداخل بين الأنظمة للحافلات أحادية الاتجاه. يستخدم المهندسون برنامج Chiplet PHY Designer لتوفير الوقت وتقليل الأخطاء، مما يضمن أن تصميماتهم تلبي متطلبات الأداء قبل التصنيع. يؤكد المتبنون الأوائل لهذا الحل، مثل Alphawave Semi، أن Chiplet PHY Designer يضمن التشغيل السلس والتوافق بين الحلول 2.5D/3D المتاحة لعملاء chiplet.

ثانه فان

[إعلان رقم 2]

المصدر: https://doanhnghiepvn.vn/cong-nghe/cong-nghe-ho-tro-thiet-ke-chip-ky-thuat-so-toc-do-cao/20250205033256204

تعليق (0)