現在、世界のチップファウンドリー業界をリードする2社は、それぞれTSMCとSamsung Foundryです。両社は2019年に極端紫外線(EUV)リソグラフィー技術をチップ製造に適用し始め、7nm未満のノードへの道を開いた。

簡単に言えば、プロセスが小さくなるほど、チップ上のトランジスタが小さくなり、処理能力とエネルギー節約が向上するため、ノードの微細化に向けた競争は、世界の主要な半導体大手の共通の競争です。

トランジスタが小型化すれば面積あたりの密度が高まります。最新のチップには最大数百億個のトランジスタが搭載されており(たとえば、3nm A17 Pro にはチップあたり最大 200 億個のトランジスタが搭載されています)、それらの間の距離は非常に狭くなければなりません。ここでEUVリソグラフィーが重要になります。この機械は世界でただ1社、オランダのASML社によって製造されています。

高NA EUVとも呼ばれる次世代の極端紫外線リソグラフィー装置の出荷が開始されました。 2025年までにTSMCとSamsung Foundryからプロセスノードの主導権を取り戻すと約束しているIntelは、開口数を0.33から0.55に増加させた4億ドル相当の新型高NA EUVマシンを最初に購入した企業である。 (NA はレンズ システムの集光能力であり、光学システムが達成できる解像度を評価するためによく使用されます)。

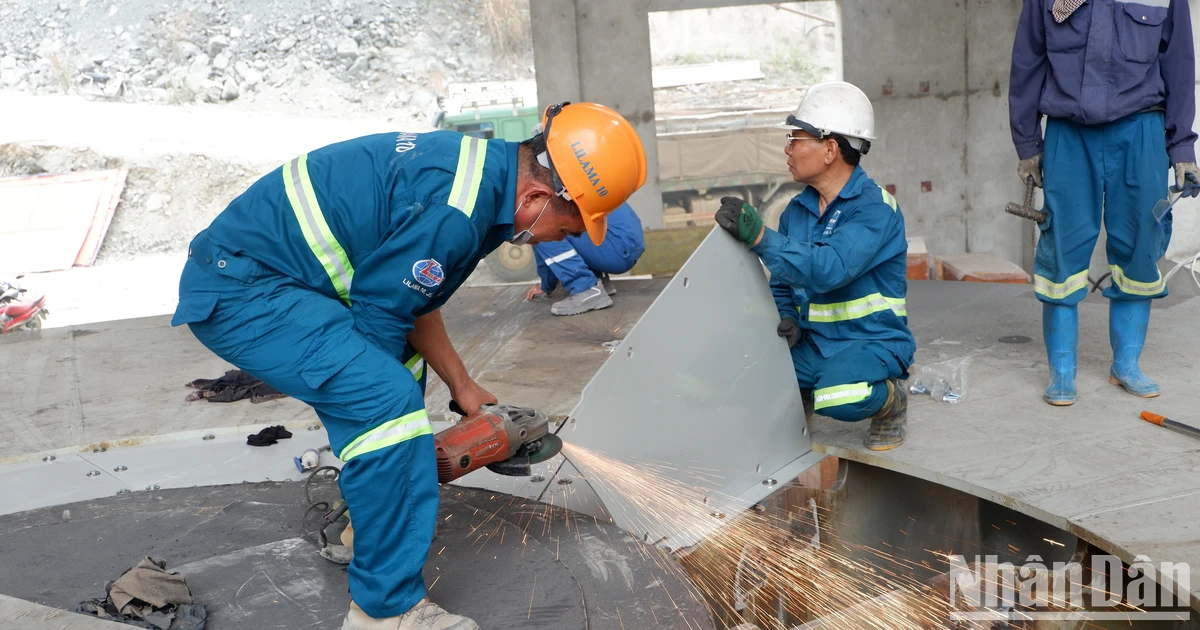

高NA EUVリソグラフィー装置が米国オレゴン州で組み立てられています。 (写真:インテル)

これにより、この機械は半導体の細部を 1.7 倍小さくエッチングできるようになり、チップのトランジスタ密度は 2.9 倍に増加します。

第 1 世代の EUV はファウンドリが 7 nm ノードを探索するのに役立ち、さらに高度な高 NA EUV マシンにより、チップ生産は 1 nm プロセス ノード、さらにはそれ以下にまで押し上げられることになります。 ASMLは、次世代マシンのNAが0.55と高いことが、新装置の性能が第一世代のEUVマシンを上回ることに貢献していると述べている。

インテルは11台の高NA EUVマシンを保有しており、最初のマシンは2025年に完成する予定だ。一方、TSMCは1.4nmプロセスノードで2028年、または1nmプロセスノードで2030年に新しいマシンを使用する計画だ。 TSMCに関しては、来年も古いEUVマシンを使用して2nmチップを生産する予定です。インテルは、高い EUV NA により、最先端のチップファウンドリ分野で TSMC や Samsung に追いつきたいと考えています。

しかし、インテルは依然として生産量の減少、財務上の損失に直面しており、株価は米国株式市場で最も強力な30銘柄で構成されるダウ工業株30種指数から除外されるほど急落している。インテルの状況は非常に悪く、3nm 以上のチップの生産を TSMC に外注せざるを得なくなりました。

中国最大のチップファウンドリーであり、TSMCとサムスンファウンドリーに次ぐ世界第3位の企業であるSMICは、米国の制裁により、第一世代のEUVリソグラフィー装置を購入することさえ許可されていない。代わりに、7nm 未満のノードのチップを製造するのに苦労する、さらに古い深紫外線 (DUV) リソグラフィー装置を使用せざるを得ません。

[広告2]

ソース

コメント (0)