DNVN - Keysight Technologies เพิ่งเปิดตัว ChipletPHY Designer 2025 โซลูชันการออกแบบชิปเล็ตดิจิทัลความเร็วสูงล่าสุด เหมาะสำหรับ AI และแอปพลิเคชันศูนย์ข้อมูล

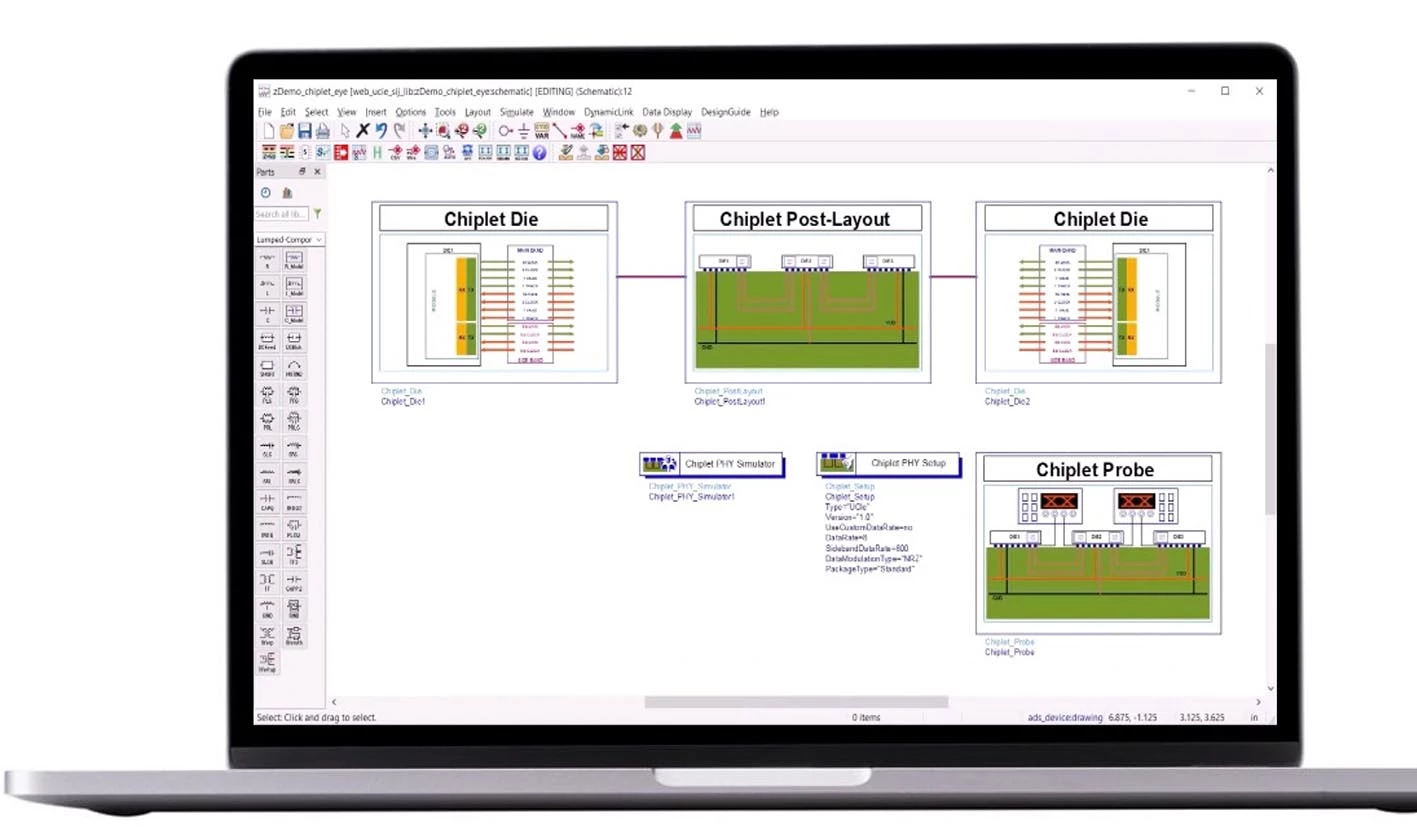

ซอฟต์แวร์ที่ได้รับการปรับปรุงนี้เพิ่มคุณสมบัติการจำลองสำหรับมาตรฐาน Universal Chiplet Interconnect Express™ (UCIe™) 2.0 และเพิ่มการรองรับสำหรับมาตรฐาน Bunch of Wires (BoW) ของ Open Computer Project Chiplet PHY Designer เป็นโซลูชันการออกแบบชิปเล็ตระดับระบบขั้นสูงและการออกแบบแบบไดทูได (D2D) ซึ่งจะช่วยให้สามารถตรวจสอบได้ในระดับก่อนซิลิคอน ทำให้ขั้นตอนการออกแบบและการผลิตชิปง่ายขึ้น

เนื่องจาก AI และชิปศูนย์ข้อมูลมีความซับซ้อนมากขึ้นเรื่อยๆ การสื่อสารที่เชื่อถือได้ระหว่างชิปจึงมีความสำคัญอย่างยิ่งในการรับรองประสิทธิภาพ

ตลาดกำลังรับมือกับความท้าทายนี้ด้วยมาตรฐานเปิดใหม่ๆ เช่น UCIe และ BoW เพื่อกำหนดการเชื่อมต่อระหว่างชิปเล็ตในบรรจุภัณฑ์แบบ 3D ที่ปรับปรุงแล้ว หรือแบบซ้อนทับ/ปรับปรุง 2.5D ด้วยการนำมาตรฐานเหล่านี้มาใช้และตรวจยืนยันความสอดคล้องของชิปเล็ต นักออกแบบจึงมีส่วนร่วมในการสร้างระบบนิเวศของการทำงานร่วมกันของชิปเล็ต ลดต้นทุนและความเสี่ยงในการพัฒนาเทคโนโลยีเซมิคอนดักเตอร์

ประโยชน์หลักของ Chiplet PHY Designer 2025: รับประกันการทำงานร่วมกันได้: ตรวจสอบว่าการออกแบบเป็นไปตามมาตรฐาน UCIe 2.0 และ BoW ช่วยให้บูรณาการได้อย่างราบรื่นทั่วทั้งระบบนิเวศการบรรจุภัณฑ์ขั้นสูง

ลดเวลาในการออกสู่ตลาด: ทำให้การจำลองและการตั้งค่าการทดสอบการปฏิบัติตามเป็นแบบอัตโนมัติ ช่วยลดความซับซ้อนของกระบวนการออกแบบชิปเล็ต

ปรับปรุงความแม่นยำในการออกแบบ: ให้ข้อมูลเชิงลึกเกี่ยวกับความสมบูรณ์ของสัญญาณ อัตราข้อผิดพลาดของบิต (BER) และการวิเคราะห์ครอสทอล์ค ลดความเสี่ยงในการออกแบบใหม่และการผลิตชิป

การออกแบบนาฬิกาที่ปรับให้เหมาะสม: รองรับการวิเคราะห์รูปแบบนาฬิกาขั้นสูง เช่น QDR อัตราข้อมูลไตรมาส เพื่อการซิงโครไนซ์ที่แม่นยำบนการเชื่อมต่อความเร็วสูง

“เมื่อปีที่แล้ว Keysight EDA ได้เปิดตัว Chiplet PHY Designer ซึ่งเป็นเครื่องมือตรวจสอบก่อนการผลิตซิลิคอนตัวแรกของตลาดที่มีคุณสมบัติการสร้างแบบจำลองและการจำลองเชิงลึก” Hee-Soo Lee หัวหน้าฝ่ายพัฒนาลูกค้าสำหรับกลุ่มผลิตภัณฑ์ดิจิทัลความเร็วสูงของ Keysight EDA กล่าว เครื่องมือนี้ช่วยให้ผู้ออกแบบชิปเล็ตตรวจสอบได้อย่างรวดเร็วว่าการออกแบบของพวกเขาเป็นไปตามข้อกำหนดก่อนการผลิต การเปิดตัวครั้งล่าสุดตรงตามมาตรฐานที่พัฒนาขึ้น เช่น UCIe 2.0 และ BoW และนำเสนอคุณลักษณะใหม่ๆ เช่น การแมปนาฬิกา QDR และการวิเคราะห์การสนทนาข้ามระบบสำหรับบัสทิศทางเดียว วิศวกรใช้ Chiplet PHY Designer เพื่อประหยัดเวลาและลดข้อผิดพลาด ช่วยให้มั่นใจว่าการออกแบบของพวกเขาตรงตามข้อกำหนดด้านประสิทธิภาพก่อนการผลิต ผู้ใช้โซลูชั่นรุ่นแรกๆ เช่น Alphawave Semi รับรองว่า Chiplet PHY Designer ช่วยให้การทำงานและการทำงานร่วมกันของโซลูชั่น 2.5D/3D ที่มีให้แก่ลูกค้าชิปเล็ตของพวกเขาราบรื่นยิ่งขึ้น

ทานห์ วาน

ที่มา: https://doanhnghiepvn.vn/cong-nghe/cong-nghe-ho-tro-thiet-ke-chip-ky-thuat-so-toc-do-cao/20250205033256204

การแสดงความคิดเห็น (0)