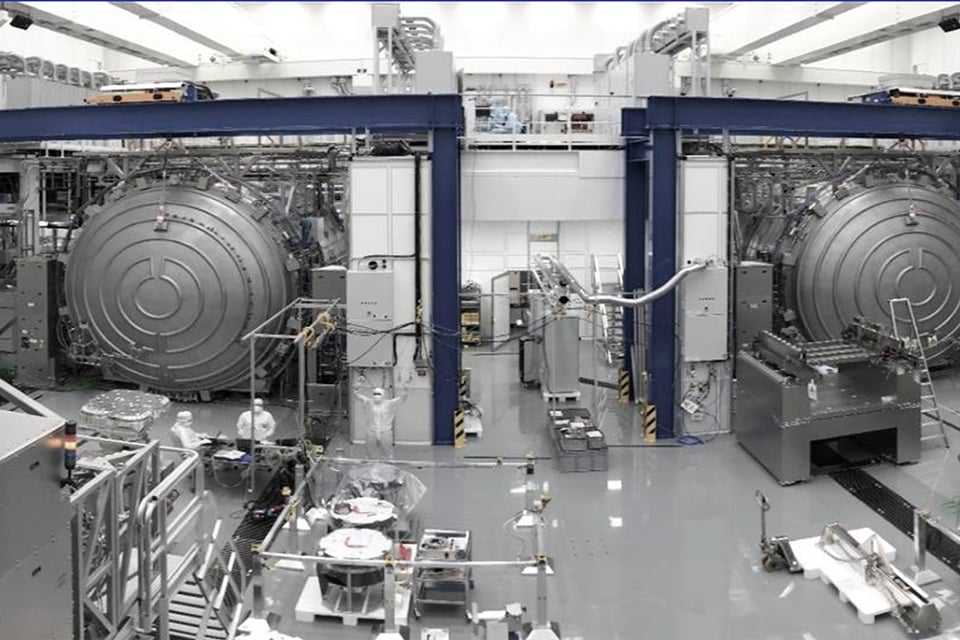

Selon PhoneArena , en 2025, TSMC et Samsung Foundry devraient commencer à produire en masse des puces de 2 nm, ce qui signifie que les puces de 1,8 nm permettront à Intel de prendre la tête des processus de fabrication de puces. Intel dépenserait entre 300 et 400 millions de dollars par machine EUV High-NA.

Chaque machine ASML High-NA coûte au moins 300 millions de dollars.

À propos de la livraison, ASML a déclaré : « Nous expédions le premier système High-NA et l'avons annoncé dans une publication sur les réseaux sociaux. Le système sera livré à Intel comme prévu, comme annoncé précédemment.

Avec les systèmes High-NA, plus le numéro NA est élevé, plus la résolution du motif gravé sur la plaquette de silicium est élevée. Alors que les machines EUV actuelles ont une ouverture de 0,33 (équivalente à une résolution de 13 nm), les machines High-NA ont une ouverture de 0,55 (équivalente à une résolution de 8 nm). Grâce au motif à plus haute résolution transféré sur la plaquette, la fonderie n'a peut-être pas besoin de faire passer la plaquette dans la machine EUV deux fois pour ajouter des fonctionnalités supplémentaires, ce qui permet d'économiser du temps et de l'argent.

Les machines EUV à haute ouverture numérique se concentrent principalement sur la réduction de la taille des transistors et l'augmentation de la densité pour intégrer davantage de transistors à l'intérieur d'une puce. Plus une puce possède de transistors, plus elle est puissante et économe en énergie. Avec les machines High-NA, les transistors peuvent être réduits de 1,7 fois avec une augmentation de la densité de 2,9 fois.

Chaque machine High-NA est expédiée par ASML dans 13 grands conteneurs

La nouvelle version de la machine High-NA EUV permettra de réaliser le processus de fabrication de puces de 2 nm et moins. La semaine dernière, TSMC et Samsung Foundry ont abordé leur feuille de route post-2 nm. Les deux entreprises prévoient de développer des semi-conducteurs en utilisant un procédé de 1,4 nm d'ici 2027. La production de puces de 2 nm devrait débuter en 2025 et, il y a quelques jours, TSMC a permis à Apple d'évaluer des prototypes de puces de 2 nm.

Le transport de la machine EUV High-NA n'était pas une tâche facile car elle était divisée en 13 grands conteneurs et 250 caisses. L’assemblage de la machine était également extrêmement difficile.

Lien source

Comment (0)