ដូច្នោះហើយ កម្មវិធីដែលបានធ្វើឱ្យប្រសើរឡើងនេះបន្ថែមលក្ខណៈពិសេសត្រាប់តាមសម្រាប់ស្តង់ដារ Universal Chiplet Interconnect Express (UCIe) 2.0 និងបន្ថែមការគាំទ្រសម្រាប់ស្តង់ដារ Bunch of Wires (BoW) របស់គម្រោងកុំព្យូទ័របើកចំហ។ ក្នុងនាមជាការរចនាបន្ទះឈីបកម្រិតប្រព័ន្ធកម្រិតខ្ពស់ និងដំណោះស្រាយរចនាស្លាប់ទៅស្លាប់ (D2D) Chiplet PHY Designer អនុញ្ញាតឱ្យមានសុពលភាពកម្រិតមុនស៊ីលីកុន ធ្វើឱ្យការរចនាបន្ទះឈីប និងដំណើរការផលិតកាន់តែងាយស្រួល។

បច្ចេកវិទ្យា Keysight ឥឡូវនេះគាំទ្រដំណោះស្រាយដំណើរការទិន្នន័យផ្សេងៗ

ដោយសារ AI និងបន្ទះឈីបមជ្ឈមណ្ឌលទិន្នន័យកាន់តែស្មុគ្រស្មាញ ការធានាទំនាក់ទំនងដែលអាចទុកចិត្តបានរវាងបន្ទះឈីបគឺមានសារៈសំខាន់ក្នុងការធានានូវដំណើរការ។ ទីផ្សារកំពុងដោះស្រាយបញ្ហាប្រឈមនេះជាមួយនឹងស្តង់ដារបើកចំហដែលកំពុងរីកចម្រើនដូចជា UCIe និង BoW ដើម្បីកំណត់ការភ្ជាប់គ្នារវាងបន្ទះសៀគ្វីក្នុង 2.5D ធ្វើឱ្យប្រសើរឡើង / 3D ឬការវេចខ្ចប់បន្ថែម / ពង្រឹង។ តាមរយៈការអនុម័តស្តង់ដារទាំងនេះ និងផ្ទៀងផ្ទាត់ការអនុលោមតាម chiplet អ្នករចនារួមចំណែកក្នុងការកសាងប្រព័ន្ធអេកូនៃអន្តរប្រតិបត្តិការ chiplet កាត់បន្ថយការចំណាយ និងហានិភ័យក្នុងការអភិវឌ្ឍន៍បច្ចេកវិទ្យា semiconductor ។

ដំណោះស្រាយនេះក៏ជួយកាត់បន្ថយពេលវេលាក្នុងការធ្វើទីផ្សារ ធ្វើឱ្យការក្លែងធ្វើស្វ័យប្រវត្តិកម្ម និងការដំឡើងការធ្វើតេស្តអនុលោមភាព ដូចជាមុខងារផ្ទេរវ៉ុល (VTF) និងសម្រួលដំណើរការរចនាបន្ទះឈីប។

"មួយឆ្នាំមុន Keysight EDA បានបើកដំណើរការ Chiplet PHY Designer ជាឧបករណ៍ផ្ទៀងផ្ទាត់មុនស៊ីលីកុនដំបូងគេរបស់ទីផ្សារជាមួយនឹងគំរូស៊ីជម្រៅ និងសមត្ថភាពក្លែងធ្វើ វាអនុញ្ញាតឱ្យអ្នករចនាបន្ទះឈីបអាចផ្ទៀងផ្ទាត់បានយ៉ាងឆាប់រហ័ស និងត្រឹមត្រូវថាការរចនារបស់ពួកគេត្រូវនឹងលក្ខណៈជាក់លាក់មុនពេលផលិត" Hee-Soo Lee ប្រធានផ្នែកអភិវឌ្ឍន៍អតិថិជនសម្រាប់ផ្នែកឌីជីថលល្បឿនលឿន EDA បាននិយាយថា Keys ។ "ការចេញផ្សាយចុងក្រោយនេះឆ្លើយតបនឹងស្តង់ដារដែលកំពុងរីកចម្រើនដូចជា UCIe 2.0 និង BoW ហើយផ្តល់នូវមុខងារថ្មីៗដូចជាការគូសផែនទីនាឡិកា QDR និងការវិភាគប្រព័ន្ធសម្រាប់រថយន្តក្រុងដែលមិនមានទិសដៅ។ វិស្វករប្រើប្រាស់ Chiplet PHY Designer ដើម្បីសន្សំសំចៃពេលវេលា និងកាត់បន្ថយកំហុស ដោយធានាថាការរចនារបស់ពួកគេបំពេញតាមតម្រូវការប្រតិបត្តិការមុនពេលផលិត។"

ប្រភព៖ https://thanhnien.vn/keysight-ra-mat-giai-phap-thiet-ke-chiplet-ky-thuat-so-toc-do-cao-moi-185250205141620491.htm

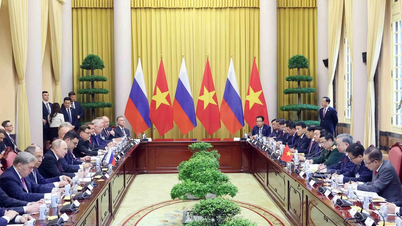

![[រូបថត] អគ្គលេខាធិកា To Lam ចាប់ផ្តើមដំណើរទស្សនកិច្ចជាផ្លូវការនៅប្រទេសរុស្ស៊ី និងចូលរួមខួបលើកទី 80 នៃជ័យជំនះលើហ្វាស៊ីសនិយម](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/5/8/5d2566d7f67d4a1e9b88bc677831ec9d)

![[រូបថត] អគ្គលេខាធិការបញ្ចប់ដំណើរទស្សនកិច្ចនៅ Azerbaijan ចាកចេញទៅទស្សនកិច្ចនៅសហព័ន្ធរុស្ស៊ី](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/5/8/7a135ad280314b66917ad278ce0e26fa)

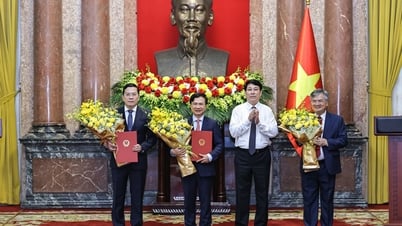

![[រូបថត] ប្រធានរដ្ឋ Luong Cuong បង្ហាញសេចក្តីសម្រេចតែងតាំងអនុប្រធានការិយាល័យប្រធានាធិបតី](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/5/8/501f8ee192f3476ab9f7579c57b423ad)

![[រូបថត] ប្រធានរដ្ឋសភាលោក Tran Thanh Man ធ្វើជាអធិបតីកិច្ចប្រជុំនៃអនុគណៈកម្មាធិការរៀបចំឯកសារនៃមហាសន្និបាតបក្សលើកទី១របស់រដ្ឋសភា។](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/5/8/72b19a73d94a4affab411fd8c87f4f8d)

![[រូបថត] នាយករដ្ឋមន្ត្រី Pham Minh Chinh ជួបជាមួយក្រុមប្រឹក្សាគោលនយោបាយស្តីពីការអភិវឌ្ឍន៍សេដ្ឋកិច្ចឯកជន](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/5/8/387da60b85cc489ab2aed8442fc3b14a)

![[រូបថត] នាយករដ្ឋមន្ត្រី Pham Minh Chinh សន្ទនាតាមទូរស័ព្ទជាមួយនាយករដ្ឋមន្ត្រីសិង្ហបុរី Lawrence Wong](https://vphoto.vietnam.vn/thumb/402x226/vietnam/resource/IMAGE/2025/5/8/e2eab082d9bc4fc4a360b28fa0ab94de)

Kommentar (0)