Dies ist eine symbolische Initiative zur Förderung der Zusammenarbeit zwischen Japan und Südkorea in dieser Branche.

Dementsprechend wird die neue Anlage mehr als 30 Milliarden Yen (222 Millionen US-Dollar) kosten und voraussichtlich in Yokohama südwestlich von Tokio errichtet werden, wo sich auch der derzeitige Hauptsitz des Samsung Research and Development Institute Japan befindet.

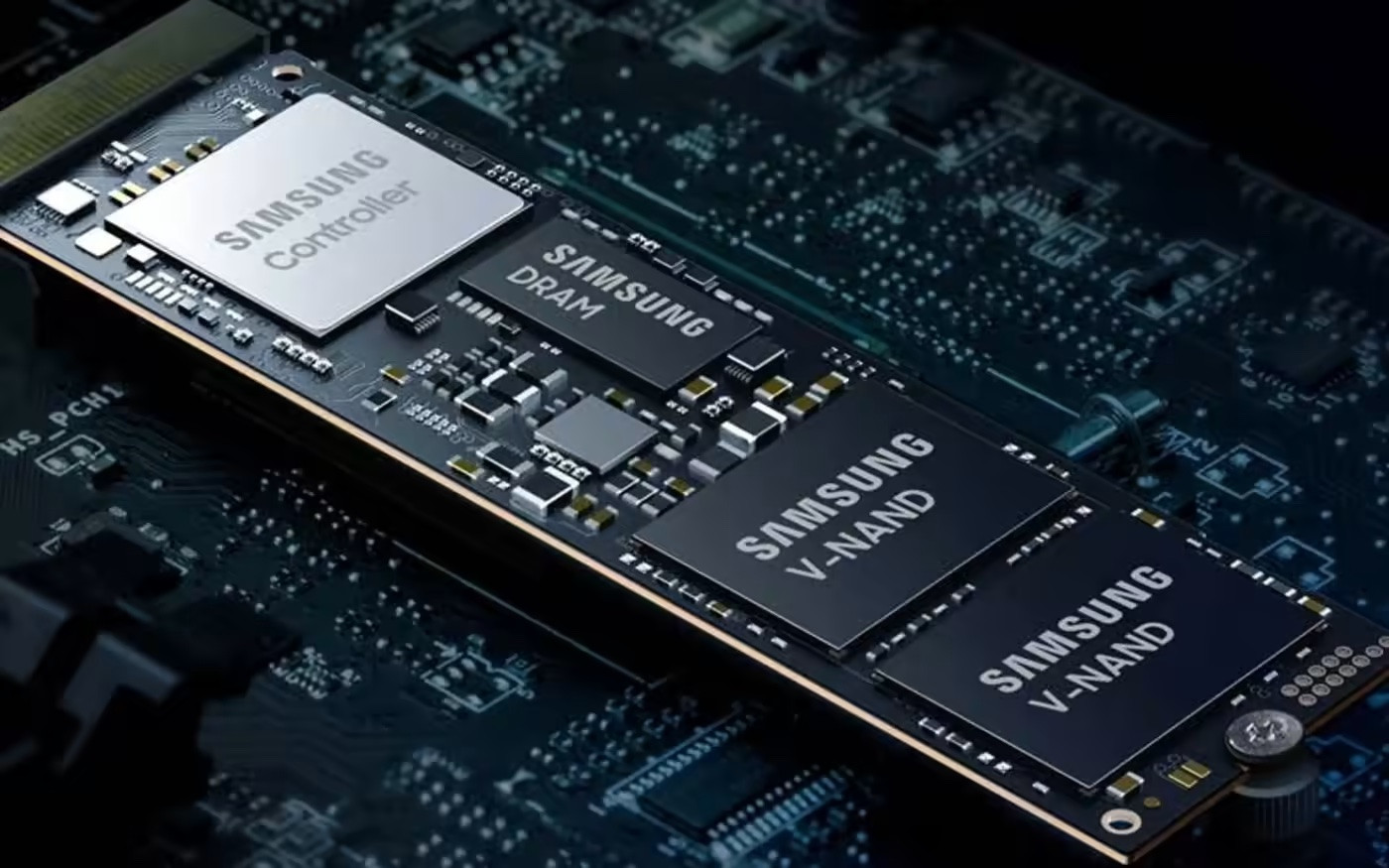

Samsung ist der weltweit größte Hersteller von Speicherchips, während Japan ein führender Produzent von Grundmaterialien für Halbleiter ist, etwa Wafern und Gießereiausrüstung.

Die neue Anlage soll bis 2025 betriebsbereit sein. Samsung möchte von den Subventionen der japanischen Regierung für den Halbleitersektor in Höhe von insgesamt über 10 Milliarden Yen profitieren.

Der Schritt des wertvollsten Unternehmens Südkoreas könnte die Zusammenarbeit zwischen den Halbleiterindustrien beider Länder fördern.

Die Investition erfolgt unmittelbar im Anschluss an eine neue Partnerschaft zwischen Seoul und Tokio unter der Führung des südkoreanischen Präsidenten Yoon Suk Yeol und des japanischen Premierministers Fumio Kishida. Es wird erwartet, dass sich die beiden Staatschefs nächste Woche am Rande des G7-Gipfels in Hiroshima treffen.

Auch Samsungs größter Konkurrent TSMC hat 2021 große Investitionen in Japan getätigt und seine Produktionsbasis diversifiziert, da Bedenken hinsichtlich einer Überkonzentration der Chipproduktion in Taiwan bestehen. TSMC unterhält außerdem eine Forschungs- und Entwicklungseinrichtung in Tsukuba, nordöstlich von Tokio.

Japan, einst weltweit führend in der Produktion von Speicherchips, versucht, seine Produktionsbasis durch die Anziehung ausländischer Investitionen wieder aufzubauen. TSMC und Micron Technology sind große ausländische Investoren in Japan und haben Subventionen von der Regierung erhalten.

Der Schwerpunkt der neuen Anlage von Samsung wird auf dem Backend der Halbleiterfertigung liegen, insbesondere auf der Verpackung von Wafern, die mit Leiterplatten in Endprodukte integriert wurden.

Traditionell konzentrierte sich die Forschung und Entwicklung auf die frühen Phasen des Herstellungsprozesses, um die Schaltkreise so weit wie möglich zu miniaturisieren. Viele sind jedoch der Ansicht, dass einer weiteren Miniaturisierung Grenzen gesetzt sind und der Schwerpunkt sich auf die Verbesserung von Back-End-Prozessen verlagern wird, etwa auf das Stapeln von Halbleiterwafern in mehreren Schichten zur Herstellung von 3D-Chips.

(Laut NikkeiAsia)

[Anzeige_2]

Quelle

![[Foto] Premierminister Pham Minh Chinh leitet Treffen zur Entwicklung von Wissenschaft und Technologie](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/5/17/ae80dd74c384439789b12013c738a045)

![[Foto] Leser stehen Schlange, um die Fotoausstellung zu besuchen und eine Sonderpublikation zum 135. Geburtstag von Präsident Ho Chi Minh bei der Nhan Dan Zeitung zu erhalten](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/5/17/85b3197fc6bd43e6a9ee4db15101005b)

![[Foto] Mehr als 17.000 Kandidaten nehmen am SPT-Kompetenzbewertungstest 2025 der Hanoi National University of Education teil](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/5/17/e538d9a1636c407cbb211b314e6303fd)

![[Foto] Fast 3.000 Studenten von Geschichten über Soldaten bewegt](https://vphoto.vietnam.vn/thumb/1200x675/vietnam/resource/IMAGE/2025/5/17/21da57c8241e42438b423eaa37215e0e)

Kommentar (0)